Looking Into The Future: How Advanced Optimization Can Manage Timelink Constraints (Part 1)

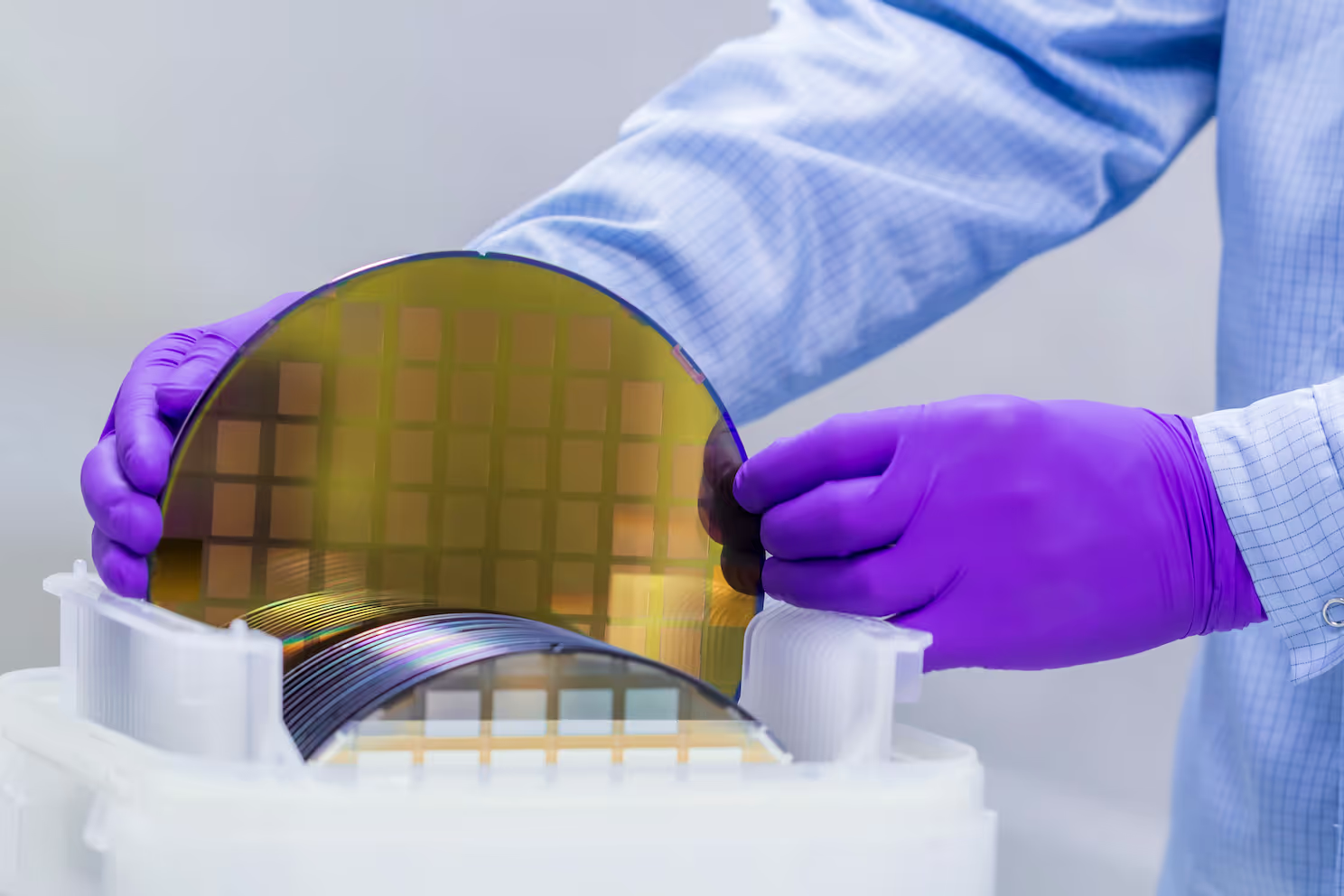

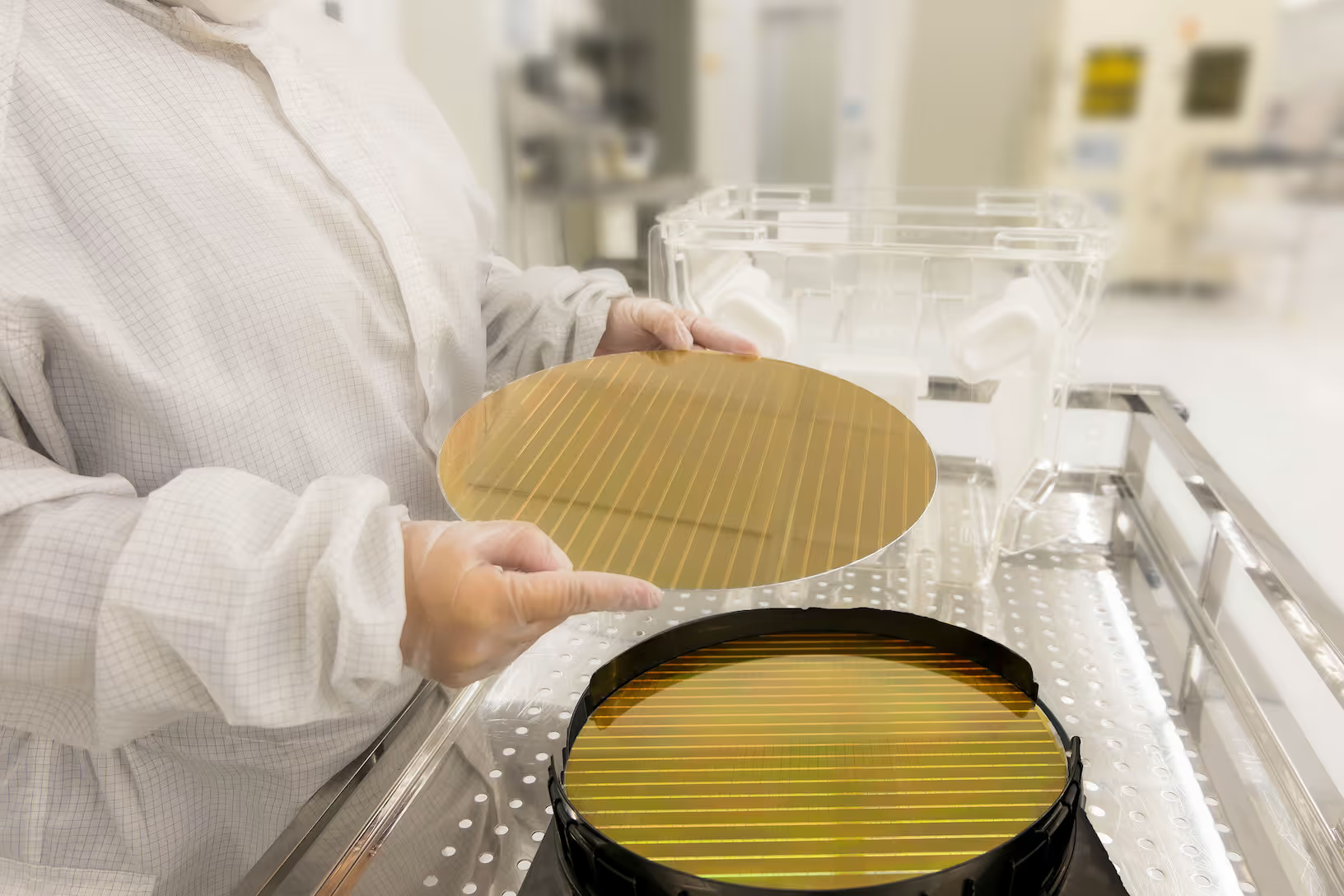

Timelinks are one of the most challenging aspects of a wafer fab to navigate and significantly increase the complexity of scheduling it. We take a dive into a case study that shows how optimization can be used to manage timelinks to alleviate pressure on bottleneck tools.

Timelinks (also known as time constraints, time lag constraints, time loops or close coupling constraints) are one of the most challenging aspects of a wafer fab to navigate and significantly increase the complexity of scheduling it. We take a dive into a case study that shows how optimization can be used to manage timelinks to alleviate pressure on bottleneck tools.

What are timelinks?

A timelink is a maximum amount of time that can elapse between two or more consecutive manufacturing process steps of a lot (a group of silicon wafers). Defining timelinks is necessary to mitigate the risk of oxidation and contamination of wafers while waiting between process steps. Violating these timelinks can lead to wafers being scrapped or undergoing a costly rework due to exposure to impurities – ramping up the production costs for a fab.

Managing timelink violations is therefore critical as its impact on cost and chip quality must be balanced with delivery speed (measured by cycle time) and other cost considerations such as leaving tools idle. When it comes to managing timelinks, most fabs look towards heuristics. However, the complexity of time constraints are difficult for a rules-based approach to navigate and require a more advanced scheduling solution. For example, deciding whether or not to dispatch a lot when the subsequent tool has a timelink requires the ability to look at the future state of tools further along the schedule. Alternatively, if you use optimization to generate a schedule then looking into the future becomes a lot more straightforward.

Using optimization to eliminate timelink violations

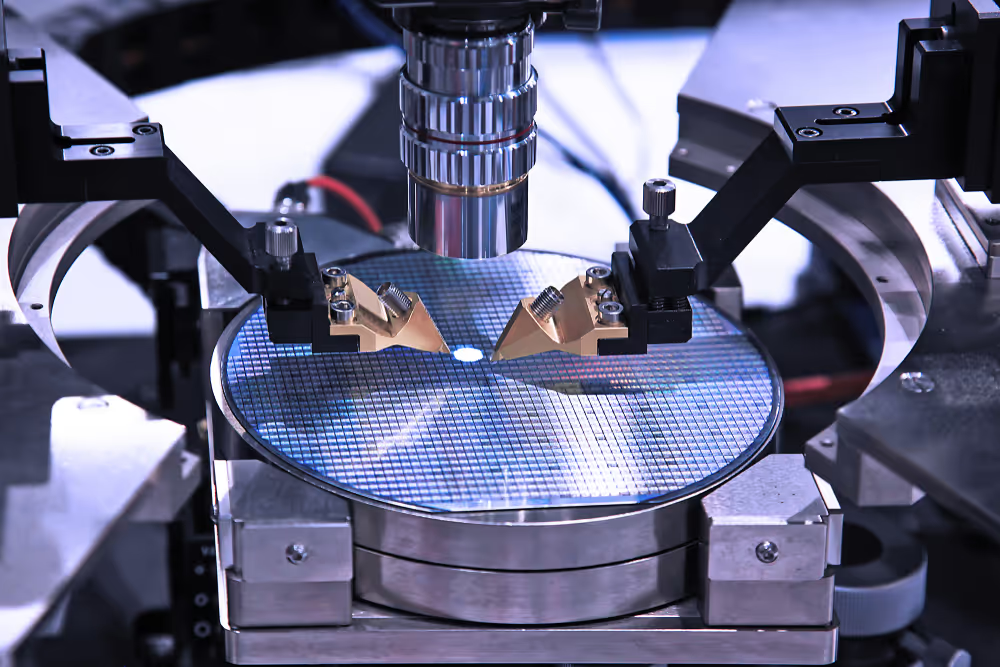

To demonstrate how optimization can help tackle the scheduling of timelinks on bottleneck tools we take a dive into a case study where scenarios are ran using Flexciton’s advanced scheduler. The case study demonstrates how timelinks at a bottleneck tool can be managed by looking several steps into the future and delaying earlier steps to more evenly balance the line.

For illustrative purposes, we consider a small problem with only 33 lots. Each lot has up to 6 remaining steps to be scheduled across 52 tools. There are time constraints of varying duration between all consecutive steps.

The sequence of process steps is defined by the product routes: A, B, C, D and ‘Other’. Routes A, B, and C all end on tool Z which is a diffusion furnace tool that runs batches of five lots at a time. All the timelinks around this tool are relatively tight at around two hours.

Case Study: Managing Timelinks at a Bottleneck Tool

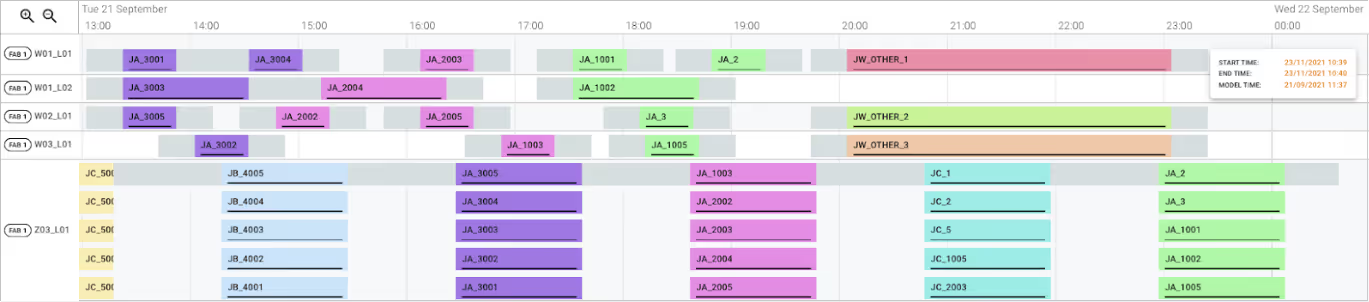

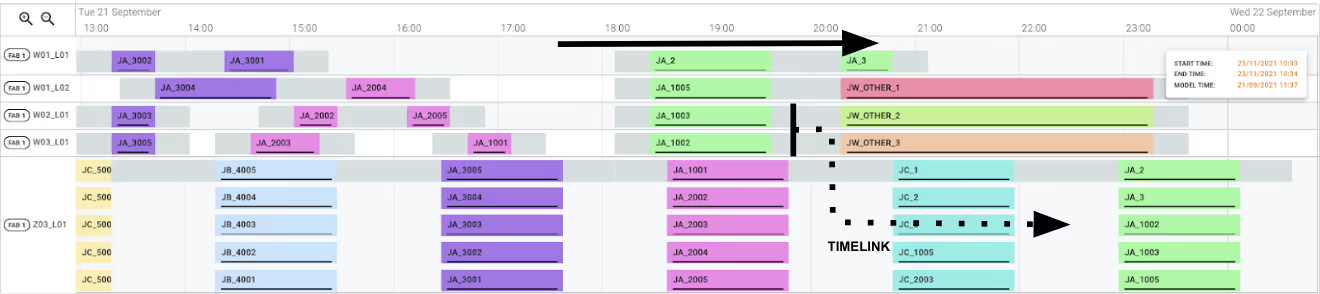

We begin by running a production schedule through Flexciton’s scheduler without considering timelinks, where we prioritise minimising cycle time alone (Fig. 1).

When timelinks are included in the schedule, we first eliminate their violations before minimising the cycle time (Fig. 2).

Figure 2 shows the light green lots (the last batch on tool Z) are shifted right on the W toolset to avoid violating timelinks on the next step, and therefore incurring the cost of scrapping wafers or performing rework. This creates a period of idle time on the W toolset and delays the other lots on W. If toolset W was considered in isolation, this solution would be suboptimal. However, when taking into account both toolsets, this provides a far better outcome.

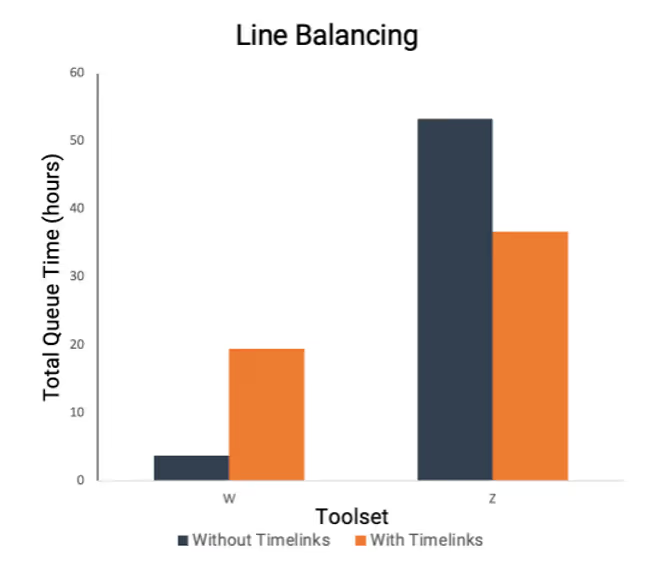

With timelinks met, we also more evenly balance queue times across the line, as demonstrated in Figure 3, which shows total queue time at the final two toolsets used in Route A in order of process steps. Toolset Z still has the highest queue time due to it being the bottleneck, but the difference is substantially reduced. This balancing reduces the bottleneck effect on tool Z.

Conclusion

This case study illustrates how using advanced optimization can help balance the line and reduce the queue time at problematic bottleneck tools. By harnessing the power of optimization we are able to assess the state of tools further down the line – something that isn’t realistically possible with traditional heuristics. This ability to significantly reduce queueing time can go a long way to helping a fab manager to hit KPIs such as the reduction of cycle time whilst avoiding costs incurred from scrapping wafers. However, the problem of scheduling timelinks becomes even more complex when you begin to consider wafers of differing priorities.

Want to learn more? Take a dive into Part 2 of this article where we will be taking a look at how to solve this problem with the added complexity of priority wafers.

More resources

Stay up to date with our latest publications.

.avif)

.avif)

.avif)